# CIFeIlows 2020-2021

# Soheil Salehi, Ph.D.

Computing Innovation Fellows

IP Owner

Side-Channe

Analysis

Defense-in-Depth

Engineering

Things (IoT)

Electrical and Computer Engineering Department, University of California, Davis

RIL

## Towards Hardware and Al-assisted Security: A Defense-In-Depth Approach

GDSII

#### ☐ ICs are more complex compared to decades ago:

- Design and fab are not handled by same entity anymore!

- ☐ High Cost of ASIC Manufacturing: Major U.S. Tech are Fabless: AMD, Nvidia,

#### ☐ Hardware security is questioned:

Qualcomm, Broadcom, etc.

- Emerging hardware security attacks

- Globalized fabrication and supply chain

The Bloomberg Businessweek. 2018. The Big Hack. Technical Report retrieved from: https://www.bloomberg.com/news/features/20 18-10-04/the-big-hack-how-china-used-a-tinychip-to-infiltrate-america-s-top-companies.

☐ Magnetic Tunnel Junctions (MTJs):

Magnetization of free layer can be modified

A tunneling oxide layer sandwiched

between two ferromagnetic layers

using a current or voltage

**Anti-Parallel**

1 (High Res)

Fixed Layer —

Bit-Line (BL)

Source-Line (SL)

Near-zero standby power

□ Advantages:

✓ Non-Volatile

Area efficient

▼ Fast read operation

**Parallel**

0 (Low Res)

Forbes. 2021. Hackers Are Targeting U.S. Banks, And Hardware May Give Them An Open Door. https://www.forbes.com/sites/roslynlayton/2021/03/ 17/hackers-are-targeting-us-banks-and-hardwaremay-give-them-an-open-door/?sh=6e3d8e8814dc

0 (Low Res)

1 (High Res)

Logic Locking via RIL-

Blocks using SyM-LUT

$E_B \approx 40 - 60 k_b T$

transfer-torque-mram-products

https://www.theregister.co.uk/

2019/03/08/samsung\_mram/

# **Key Contributions:**

- ✓ Defense-in-Depth for Hardware Security

- ✓ Symmetrical MRAM-LUT (SyM-LUT):

- Utilize emerging post-CMOS devices

- Low power variation mitigates P-SCAs

- Scan Obfuscation Mechanism (SOM)

- Reliable in presence of Process Variation

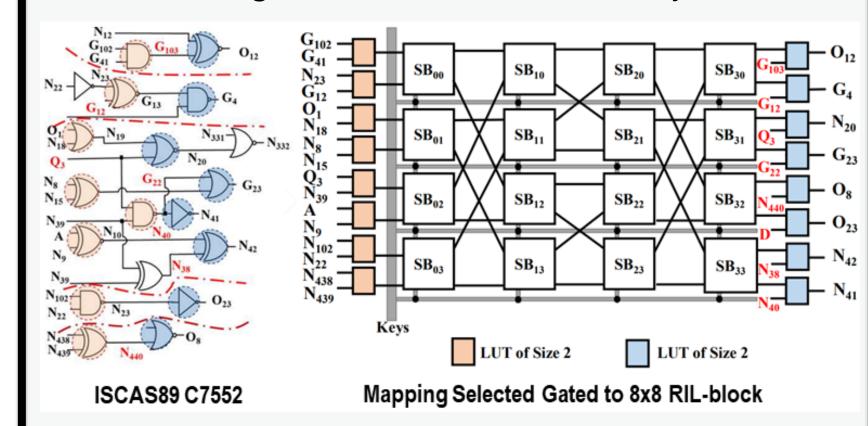

- ✓ Reconfigurable Interconnect and Logic-**Blocks (RIL-Blocks):**

- Combination of LUTs and logarithmic network

- High output corruptibility for SAT-resiliency

- SAT-resiliency with few 8x8x8 RIL-blocks Low overhead using 2-input SyM-LUTs

- ✓ Thwarts bypass and removal attacks

### ✓ Dynamic morphing capability **Design Engineer SAT-resilient** Side-Channel SAT-based **Attack**

#### Comparison of Security Coverage with state-of-the-art attacks

| Attacks                   | SFLL     | GSHE/MESO    | InterLock    | CAS-Lock     | LUT          | Proposed     |

|---------------------------|----------|--------------|--------------|--------------|--------------|--------------|

| Tittacks                  | [1]      | [2,3]        | [4]          | [5]          | [6]          | Froposed     |

| SAT-attack                | <b>✓</b> | X            | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     |

| AppSAT                    | <b>✓</b> | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ✓            |

| Power side channel attack | -        | -            | -            | _            | _            | ✓            |

| Removal attack            | ✓        | _            | $\checkmark$ | $\checkmark$ | $\checkmark$ | <b>1</b>     |

| ScanSAT                   | _        | _            | _            | _            | $\checkmark$ | ✓            |

| Shift and Scan attack     | -        | -            | -            | -            | $\checkmark$ | $\checkmark$ |

| Features                  | [1]      | [2,3]        | [4]          | [5]          | [6]          | Proposed     |

| Dynamic morphing          | X        | <b>√</b>     | X            | X            | X            | <b>√</b>     |

| Application               | -        | Limited      | -            | -            | -            | -            |

|                           |          |              |              |              |              |              |

#### □ RIL-Blocks:

Combination of LUTs with almost nonblocking Banyan network with  $(N/2) \log_2 N$ switching blocks for SAT resiliency.

#### □ Design Questions:

- Insertion Policy: Can be inserted randomly

- Design Complexity: as low as 3 RIL-blocks

- **LUT Complexity**: LUT-2 for small overhead

Size and Quantity of RIL-blocks for ISCAS C7552 Benchmark for SAT-resiliency

|            | Size of RIL Blocks |         |          |            | Size of RIL Blocks |          |          |

|------------|--------------------|---------|----------|------------|--------------------|----------|----------|

| RIL Blocks | 2x2                | 8x8     | 8x8x8    | RIL Blocks | 2x2                | 8x8      | 8x8x8    |

| 1          | 0.31               | 0.63    | 23.53    | 10         | 1.16               | $\infty$ | $\infty$ |

| 2          | 0.35               | 6.33    | 198.556  | 25         | 34.5               | $\infty$ | $\infty$ |

| 3          | 0.405              | 20.422  | $\infty$ | 50         | 102.319            | $\infty$ | $\infty$ |

| 4          | 0.55               | 180.938 | $\infty$ | 75         | $\infty$           | $\infty$ | $\infty$ |

| 5          | 0.67               | 316.231 | $\infty$ | 100        | $\infty$           | $\infty$ | $\infty$ |

|            |                    |         |          |            |                    |          |          |

#### ☐ SAT-Attack:

State-of-the-art SAT-Attacks with CaDiCaL<sup>1</sup>

■ Benchmarks: ISCAS-89<sup>2</sup> and DoD's Common Evaluation Platform (CEP)<sup>3</sup>

Comparison of ML-assisted P-SCAs on SyM-LUT with SOM

| Benchmark | Benchmark | Number of RIL-Block |          |          | AppSAT  |

|-----------|-----------|---------------------|----------|----------|---------|

| Suite     | Circuit   | 1                   | 2        | 3        | Success |

| ISCAS-89  | b15       | 124.25              | 546.2    | $\infty$ | X       |

|           | s35932    | 105.1               | 1864.2   | $\infty$ | ×       |

|           | s38584    | 345.2               | $\infty$ | $\infty$ | ×       |

|           | b20       | 240.4               | 2454.26  | $\infty$ | ×       |

|           | AES       | 1060.56             | $\infty$ | $\infty$ | ×       |

| CEP       | SHA-256   | 846.87              | $\infty$ | $\infty$ | ×       |

|           | MD5       | 1450.1              | $\infty$ | $\infty$ | ×       |

|           | GPS       | $\infty$            | $\infty$ | $\infty$ | ×       |

#### ☐ Machine Learning-Assisted P-SCA:

- Dataset: 640,000 power traces for 16 labels

- 16(Gates)x4(Keys/Gate)x10,000 instances Evaluation metric: Accuracy and F1-score

- Feature scaling and outlier filtering: z-

- scores for data pre-processing

#### Comparison of ML-assisted P-SCAs on SyM-LUT with SOM Algorithm F1-Score Accuracy

| 7 Hgorrenn          | riccuracy | 11 50010 |  |

|---------------------|-----------|----------|--|

| Random Forest       | 31.6%     | 0.322    |  |

| Logistic Regression | 30.93%    | 0.310    |  |

| SVM                 | 26.36%    | 0.284    |  |

| DNN                 | 35.01%    | 0.357    |  |

|                     |           |          |  |

1. Armin Biere. SAT Competition-2018.

2. Available at: <a href="https://pld.ttu.ee/~maksim/benchmarks/">https://pld.ttu.ee/~maksim/benchmarks/</a>

3. CEP is a system on a chip design that is representative of typical microelectronics used by the body of the Department of Defense (DoD) and includes instrumentation and government-specific benchmarks.

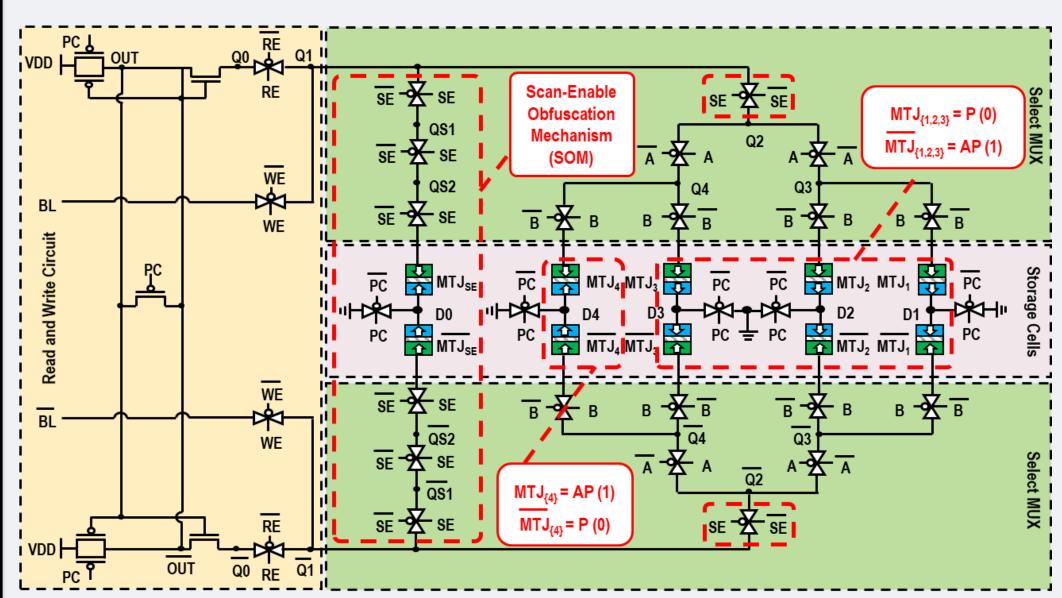

#### ☐ Symmetrical MRAM-LUTs (SyM-LUT):

- P-SCA resiliency using emerging spin-based devices

- Scan Obfuscation Mechanism (SOM)

#### ☐ HSPICE Simulation:

- 45nm PTM CMOS Technology<sup>1</sup>

- STT-MRAM Verilog A Model<sup>2</sup>

■ 10,000 MC for PV analysis<sup>3</sup>

OUT (0110) B (1100) XOR Gate A (1010) MTJ<sub>SE</sub> (1) / MTJ<sub>SE</sub> 0-3ns Write MTJ<sub>1</sub>  $MTJ_4(0) / \overline{MTJ}_4$ 6-9ns 9-12ns  $MTJ_3(1) / \overline{MTJ}_3$ 12-15ns Write MTJ<sub>SI</sub> 16-16.5ns Read MTJ<sub>1</sub>  $MTJ_2(1) / \overline{MTJ}_2$ 17-17.5ns Read MTJ<sub>2</sub> 18-18.5ns Read MTJ<sub>3</sub>  $MTJ_1(0) / \overline{MTJ_1}$ 19-19.5ns Read MTJ<sub>4</sub> 10ns 15ns

#### ☐ Energy of 2-input SyM-LUT:

- Standby Energy: 20aJ

- Write Energy: 33fJ

- Read Energy: 4.6fJ

#### □ Reliability of 2-input SyM-LUT:

Sample read current traces for the proposed 2-input SyM-LUT

configured to implement different logic functions.

- 640,000 error-free read/write

- P (M=32.7KΩ) << AP (M=57.7KΩ)

- □ Area vs. 2-input SRAM-LUT:

- Select MUX: +12 transistors

- Storage Cell: -20 transistors

- SOM: +18 transistors

1. 45nm Predictive Technology Model (PTM), Available at: <a href="http://ptm.asu.edu/">http://ptm.asu.edu/</a>. 2. J. Kim, et al., "A technology-agnostic MTJ SPICE model with user-defined dimensions for STT-MRAM scalability studies," IEEE Custom Integrated Circuits Conference (CICC), 2015, pp. 1-4. 3. S. Salehi, et al., "Clockless Spin-based Look-Up Tables with Wide Read Margin," Great Lakes Symposium on VLSI (GLSVLSI), 2019, pp. 363-366.

#### **Acknowledgement:**

This material is based upon work supported by the National Science Foundation (NSF) under grant Computing Research Association for CIFellows Project 2030859. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the NSF.

#### References:

[1] M. Yasin, et al., "SFLL-HLS: Stripped-functionality logic locking meets high-level synthesis," in 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2019, pp. 1–4. [2] B. Shakya, et al., "CAS-Lock: A security-corruptibility trade-off resilient logic locking scheme," ACR

Transactions on Cryptographic Hardware and Embedded Systems, pp. 175-202, 2020.

[3] N. Rangarajan, et al., "Opening the doors to dynamic camouflaging: Harnessing the power of polymorphic devices," IEEE Transactions on Emerging Topics in Computing (TETC), p. 1–1, 2020. [4] H. M. Kamali, et al., "Interlock: An intercorrelated logic and routing locking," in IEEE/ACM International

Conference on Computer-Aided Design (ICCAD), 2020. [5] G. Kolhe, et al., "Security and complexity analysis of LUT-based obfuscation: From blueprint to reali in IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2019, pp. 1–8.

[6] S. P.et al., "Advancing hardware security using polymorphic and stochastic spin-hall effect devices," 2018 Design, Automation Test in Europe Conference Exhibition (DATE), 2018, pp. 97–102.